Computer Architecture Lab/SS2013/Group3/Assignment1

Description of the microcontroller architectures

[edit | edit source]AVR

[edit | edit source]Although the AVR architecture comes in 3 main families of microcontrollers, plus other more specialized series, we will be discussing the AVR32 architecture. This architecture is a reduced instruction set computer (RISC) with a 32-bit datapath

Architecture

[edit | edit source]- data path on 32 bits

- 3 to 7 stage pipeline

- 15 general purpose registers

- Big endianness

- non-volatile flash memory for the program memory (has the advantage that the microcontroller keeps its program even after a power outage)

- data memory consists of the register file, the I/O registers (for controlling the different peripherals on the microcontroller) and a SRAM memory

- almost all AVR microcontroller have an internal EEPROM, which is for semi-permanent data storage

- execution stage works in register-to-register mode

Instruction Set

[edit | edit source]| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Instruction |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | d d d d | r r r r | MOVW Move register pair | ||||||

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | d d d | r r r | Signed and fractional multiply (R16–R23 only) | |||||||

| 0 | 0 | 0 | 0 | 0 | 1 | r | d d d d d | r r r r | 2-operand instructions CPC, SBC, ADD, CPSE, CP, SUB. ADC, AND, EOR, OR, MOV | |||||||

| 0 | 0 | 0 | 0 | 1 | ||||||||||||

| 0 | 0 | 0 | 1 | |||||||||||||

| 0 | 0 | 1 | 0 | |||||||||||||

| 0 | 0 | 1 | 1 | K K K K | h h h h | K K K K | Register-immediate instructions CPI, SBCI, SUBI, ORI, ANDI | |||||||||

| 0 | 1 | |||||||||||||||

| 1 | 0 | k | 0 | k k | s | d d d d d | y | k k k | LDD/STD to Z+k or Y+k | |||||||

| 1 | 0 | 0 | 1 | 0 | 0 | s | d d d d d | LD/ST other | ||||||||

| 1 | 0 | 0 | 1 | 0 | 1 | 0 | d d d d d | 0 | 1-operand instructions (COM, NEG, SWAP, etc.) | |||||||

| 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | B̅ | b b b | 1 | 0 | 0 | 0 | SEx/CLx Status register clear/set bit | ||

| 1 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | Misc instructions (RET, RETI, SLEEP, etc.) | ||||

| 1 | 0 | 0 | 1 | 0 | 1 | 0 | c | 0 | 0 | 0 | 1 | 0 | 0 | 1 | Indirect jump/call to Z or EIND:Z | |

| 1 | 0 | 0 | 1 | 0 | 1 | 0 | d d d d d | 1 | 0 | 1 | 0 | DEC Rd | ||||

| 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | k k k k | 1 | 0 | 1 | 1 | DES round k | |||

| 1 | 0 | 0 | 1 | 0 | 1 | 0 | k k k k k | 1 | 1 | c | k | JMP/CALL abs22 | ||||

| 1 | 0 | 0 | 1 | 0 | 1 | 1 | k k | p p | k k k k | ADIW/SBIW Rp,uimm6 | ||||||

| 1 | 0 | 0 | 1 | 1 | 0 | B | a a a a a | b b b | I/O space bit operations | |||||||

| 1 | 0 | 0 | 1 | 1 | 1 | r | d d d d d | r r r r | MUL, unsigned: R1:R0 = Rr×Rd | |||||||

| 1 | 0 | k | 0 | k k | s | d d d d d | y | k k k | See 10k0 above

| |||||||

| 1 | 0 | 1 | 1 | s | a a | d d d d d | a a a a | OUT/IN to I/O space | ||||||||

| 1 | 1 | 0 | c | 12 bit signed offset | Relative jump/call to PC ± 2×simm12 | |||||||||||

| 1 | 1 | 1 | 0 | K K K K | h h h h | K K K K | LDI Rh,K | |||||||||

| 1 | 1 | 1 | 1 | 0 | B̅ | 7-bit signed offset | b b b | Conditional branch on status register bit | ||||||||

| 1 | 1 | 1 | 1 | 1 | 0 | s | d d d d d | 0 | b b b | BLD/BST register bit to STATUS.T | ||||||

| 1 | 1 | 1 | 1 | 1 | 1 | B | d d d d d | 0 | b b b | SBRC/SBRS skip if register bit equals B | ||||||

ARM

[edit | edit source]Based on the high market share of the ARM-based chips, we can safely say that it is the most used reduced instruction set computer (RISC) today.

Architecture

[edit | edit source]- data path on 32 or 64 bits

- 3 stage pipeline (up to ARM7 version), up to 13 stages for higher performance versions

- 16 general purpose registers, some having special function (e.g. Stack Pointer, Link Register, Program Counter)

- Bi-endianness, with little endian as default

- support for 16 coprocessors, connected in a non-intrusive way

- floating point based on VPF (Vector Floating Point) technology, as coprocessor

- execution stage works in register-to-register mode

Instruction Set

[edit | edit source]- ARM relies on a load/store architecture

- 32-bit wide instructions

- mostly single clock cycle execution

- link register for fast leaf function calls

- 2 priority level interrupt subsystem

- supports add, subtract and multiply instructions, with some cores implementing integer divide

- fold shifts/rotates into the data processing, reducing memory accesses and therefore improving pipeline efficiency

MIPS

[edit | edit source]MIPS (originally an acronym for Microprocessor without Interlocked Pipeline Stages) is a reduced instruction set computer (RISC) instruction set architecture (ISA) developed by MIPS Technologies (formerly MIPS Computer Systems, Inc.). Early versions had a 32-bit wide datapath, with latter ones at 64-bit.

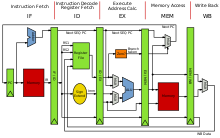

Architecture (considering R2000 version)

[edit | edit source]

- data path on 32 bits

- 5 pipeline stages:

- Instruction Fetch

- Instruction Decode

- Execute

- Memory read/store

- Writeback

- 32 32-bit general purpose registers (GPR)

- could be booted either as big-endian or little-endian

- support for up to 4 co-processors

- could plug in the R2010 Floating Point Unit (FPU), having 32 32-bit registers (which could be used as 16 64-bit registers, for double precision)

- external SRAM cache

- internal DRAM (very slow writing time)

- execution stage is of type register-to-register, the ALU obtaining values from the register file and writing back to the register file during writeback stage

Instruction Set

[edit | edit source]We are assuming an 32-bit MIPS processor, therefore the instruction size is of 32 bits. The instruction set is based around 3 types of instructions:

- R - for operations based around values in the registers (arithmetic, logical, data transfer, unconditional jump register)

- I - for operations based around values in the registers as well as an immediate value

- J - for jump instructions, having only an immediate value specified (due to the need of all 26 bits for the address space)

Instruction formats are as follows:

| Type | 31 format (bits) 0 | |||||

|---|---|---|---|---|---|---|

| R | opcode (6) | rs (5) | rt (5) | rd (5) | shamt (5) | funct(6) |

| I | opcode (6) | rs (5) | rt (5) | immediate (16) | ||

| J | opcode (6) | address (26) | ||||

For the complete list of instructions check this link.