UTPA STEM/CBI Courses/Microprocessor Systems/Microprocessor System Design

Course Title: Microprocessor System Design

Lecture Topic: Cache Memory Design

Instructor: Dr. Yul Chu

Institution: University of Texas - Pan American

Backwards Design

[edit | edit source]Course Objectives

- Primary Objectives- By the next class period students will be able to:

- Sub Objectives- The objectives will require that students be able to:

- Understand how the read memory operation works.

- Understand how the write memory operation works.

- Difficulties- Students may have difficulty:

- To understand how to access cache memory with memory address.

- To understand how to replace the block data from memory to cache memory.

- Real-World Contexts- There are many ways that students can use this material in the real-world, such as:

- Intel x86 CISC microprocessor

- MIPS 2000 RISC processor

Model of Knowledge

- Concept Map

- Determining a cache size

- Determining a block size

- Understanding mapping functions

- Understanding replacement policies

- Understanding write policies

- Content Priorities

- Enduring Understanding

- Direct-mapped, n-way set-associative, and fully associative

- Least Recently Used (LRU), Most Recently Used (MRU), and Random replacement policies

- Write-Back/Write-Allocate and Write-Through/Write-No-Allocate policies

- Important to Do and Know

- How to access cache memory with index part of memory address.

- How to replace a cache line based on dirty bit info.

- The concept of block data and byte offset is ?

- Worth Being Familiar with

- Understanding cache memory and memory locations

- Computing average memory access time

- Understanding block address and data in cache memory

- Enduring Understanding

Assessment of Learning

- Formative Assessment

- In Class (groups)

- Let each group (3 to 4 students/group) design a cache memory and discuss it.

- Let each group check the five factors for a cache memory and verify it.

- Homework (individual)

- To implement some memory references manually.

- To compute average memory access time for direct-mapped and n-way set-associative cache memory.

- In Class (groups)

- Summative Assessment

- Let each group design a cache memory (4-way set-associative) and implement several read and write operations.

- Final Exam

Legacy Cycle

[edit | edit source]OBJECTIVE

By the next class period, students will be able to:

- Understand how the read memory operation works

- Understand how the write memory operation works.

- Understand why the temporal and spatial localities are important to design a cache memory.

The objectives will require that students be able to:

- Understand memory hierarchy.

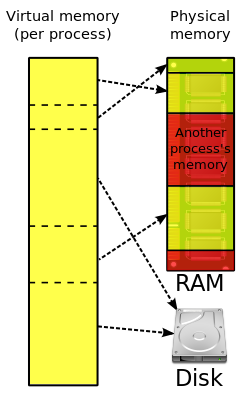

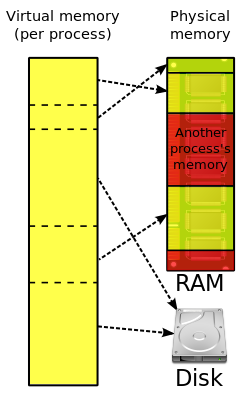

- Understand physical memory and virtual memory.

The program thinks it has a large range of contiguous addresses; but in reality the parts it is currently using are scattered around memory (RAM), and the inactive parts are saved in a disk file. - Understand how the mapping function works.

- Understand how the replacement policy works.

- Understand how the writing policy works.

THE CHALLENGE

How to design cache memory to reduce cache misses for a small L1 cache to improve system performance?

GENERATE IDEAS

How to design a cache memory using localities?

MULTIPLE PERSPECTIVES

How to implement 'write hit and miss policies'? How to implement 'LRU replacement policy for 2-way or 4-way set-associative cache memories'? How to update the cache memory for a write-back? How to access a cache memory from processor?

RESEARCH & REVISE

-Read lecture notes, textbook, and papers. -group discussion. -do manual implementation and revise any errors.

TEST YOUR METTLE

- Formative assessment: Small quizzes, concept quizzes, and discussion.

- Summative Assessment: Projects and exam.

GO PUBLIC

Final presentation, report, grading, and verification test.

Pre-Lesson Quiz

[edit | edit source]- What is the purpose of cache memory?

- Is it possible to access cache memory with memory address? If yes, how?

- What does SRAM stand for?

- What does RAM stand for?

- Which one is more expensive, RAM or SRAM ?

- What is L1 (Level One) cache?

- What is Temporal Locality?

- Explain Fetch-Execute cycle.

- Explain the differences between RISC and CISC.

- What is Spatial Locality?

Test Your Mettle Quiz

[edit | edit source]- Why the performance of 2-way set-associative has better performance than direct-mapped cache?

- Which of the following replacement policies is popular and why? 1) LRU 2)MRU 3) Random

- For a small cache memory, which of the following cache misses is critical to performance? 1) Conflict miss 2) Compulsory miss 3) Capacity miss

- What kind of write-miss policy can work with write-back hit policy?

- List 5 factors to design cache memory.

- List three steps to determine cache miss or hit?

- What is memory hierarchy?

- Explain physical address and virtual address in brief.

- What are the benefits of the virtual address?

- If the size of a direct-mapped cache memory is 8KB and the block size is 64 bytes, then how many bits for cache indexing are needed?