Materials Science and Engineering/Doctoral review questions/Daily Discussion Topics/01172008

Silicide

[edit | edit source]Motivation to use silicide:

- Diffusion barrier

- Low contact resistance

- The contact resistance is determined by the work function difference

- A silicide reduces the contact resistance

- The basis of the work function and conductivity are different

Transition Metals

[edit | edit source]Transition metals commonly refers to any element in the d-block of the periodic table, including zinc, cadmium and mercury. This corresponds to groups 3 to 12 on the periodic table.

A solid circle represents a common oxidation state, and a ring represents a less common (less energetically favourable) oxidation state.

Properties

[edit | edit source]Transition elements tend to have high tensile strength, density and melting and boiling points. As with many properties of transition metals, this is due to d orbital electrons' ability to delocalise within the metal lattice. In metallic substances, the more electrons shared between nuclei, the stronger the metal.

There are several common characteristic properties of transition elements:

- They often form colored compounds.

- They can have a variety of different oxidation states.

- At least one of their compounds has an incomplete d-electron subshell.

- They are often good catalysts.

- They are silvery-blue at room temperature (except copper and gold).

- They are solids at room temperature (except mercury).

- They form complex ions (aqua ions included).

- They are often paramagnetic.

Work Function

[edit | edit source]The work function is the minimum energy (usually measured in electron volts) needed to remove an electron from a solid to a point immediately outside the solid surface (or energy needed to move an electron from the Fermi energy level into vacuum). Here "immediately" means that the final electron position is far from the surface on the atomic scale but still close to the solid on the macroscopic scale. The work function is an important property of metals. The magnitude of the work function is usually about a half of the ionization energy of a free atom of the metal.

Ionization Energy

[edit | edit source]

The ionization potential, ionization energy or of an atom or molecule is the energy required to remove one mole of electrons from one mole of isolated gaseous atoms or ions. More generally, the nth ionization energy is the energy required to strip it of an nth mole of electrons after the first n − 1 mole of electrons have already been removed. It is considered in physical chemistry as a measure of the "reluctance" of an atom or ion to surrender an electron, or the "strength" by which the electron is bound; the greater the ionization energy, the more difficult it is to remove an electron. The ionization potential is an indicator of the reactivity of an element. Elements with a low ionization energy tend to be reducing agents and to form salts.

Alkali Metals

[edit | edit source]The alkaline metals are a series of elements comprising Group 1 (IUPAC style) of the periodic table: Lithium (Li),sodium (Na), potassium (K), rubidium (Rb), cesium (Cs), and francium (Fr). (Note that hydrogen, although nominally also a member of Group 1, very rarely exhibits behavior comparable to the alkali metals). The alkali metals provide one of the best examples of group trends in properties in the periodic table, with well characterized homologous behavior down the group.

The alkali metals are all highly reactive and are rarely found in elemental form in nature. As a result, in the laboratory they are stored under mineral oil. They also tarnish easily and have low melting points and densities. Potassium and rubidium possess a weak radioactive characteristic (harmless) due to the presence of long duration radioactive isotopes.

The alkali metals are silver-colored (cesium has a golden tinge), soft, low-density metals, which react readily with halogens to form ionic salts, and with water to form strongly alkaline (basic) hydroxides. These elements all have one electron in their outermost shell, so the energetically preferred state of achieving a filled electron shell is to lose one electron to form a singly charged positive ion, or cation.

Hydrogen, with a solitary electron, is usually placed at the top of Group 1 of the periodic table, but it is not considered an alkali metal; rather it exists naturally as a diatomic gas. Removal of its single electron requires considerably more energy than removal of the outer electron for the alkali metals. As in the halogens, only one additional electron is required to fill in the outermost shell of the hydrogen atom, so hydrogen can in some circumstances behave like a halogen, forming the negative hydride ion. Binary compounds of hydride with the alkali metals and some transition metals have been prepared. Under extremely high pressure, such as is found at the core of Jupiter, hydrogen does become metallic and behaves like an alkali metal; see metallic hydrogen.

Alkali metals have the lowest ionization potentials in their respective periods, as removing the single electron from the outermost shell gives them the stable inert gas configuration. But their second ionization potentials are very high, as removing an electron from a species having a noble gas configuration is very difficult.

Alkali metals are famous for their vigorous reactions with water, and these reactions become increasingly violent as one moves down the group. The reaction with water is as follows:

Alkali metal + water → Alkali metal hydroxide + hydrogen gas

MOSFET

[edit | edit source]Metal-Oxide-Semiconductor Structure

[edit | edit source]

A traditional metal–oxide–semiconductor (MOS) structure is obtained by depositing a layer of silicon dioxide (SiO2) and a layer of metal (polycrystalline silicon is commonly used instead of metal) on top of a semiconductor die. As the silicon dioxide is a dielectric material its structure is equivalent to a planar capacitor, with one of the electrodes replaced by a semiconductor.

When a voltage is applied across a MOS structure, it modifies the distribution of charges in the semiconductor. If we consider a P-type semiconductor (with NA the density of acceptors, p the density of holes; p = NA in neutral bulk), a positive voltage, VGB, from gate to body (see figure) creates a depletion layer by forcing the positively charged holes away from the gate-insulator/semiconductor interface, leaving exposed a carrier-free region of immobile, negatively charged acceptor ions. See doping (semiconductor). If VGB is high enough, a high concentration of negative charge carriers forms in an inversion layer located in a thin layer next to the interface between the semiconductor and the insulator. (Unlike the MOSFET, discussed below, where the inversion layer electrons are supplied rapidly from the source/drain electrodes, in the MOS capacitor they are produced much more slowly by thermal generation through carrier generation and recombination centers in the depletion region.) Conventionally, the gate voltage at which the volume density of electrons in the inversion layer is the same as the volume density of holes in the body is called the threshold voltage.

This structure with P-type body is the basis of the N-type MOSFET, which requires the addition of an N-type source and drain regions.

Gate Material

[edit | edit source]The primary criterion for the gate material is that it is a good conductor. Highly-doped polycrystalline silicon is an acceptable, but certainly not ideal conductor, and it also suffers from some more technical deficiencies in its role as the standard gate material. Nevertheless, there are several reasons favoring use of polysilicon as a gate material:

- The threshold voltage (and consequently the drain to source on-current) is modified by the work function difference between the gate material and channel material. Because polysilicon is a semiconductor, its work function can be modulated by adjusting the type and level of doping. Furthermore, because polysilicon has the same bandgap as the underlying silicon channel, it is quite straightforward to tune the work function, so as to achieve low threshold voltages for both NMOS and PMOS devices. By contrast the work functions of metals are not easily modulated, so tuning the work function to obtain low threshold voltages becomes a significant challenge. Additionally, obtaining low threshold devices on both PMOS and NMOS devices would likely require the use of different metals for each device type, introducing additional complexity to the fabrication process.

- The Silicon-SiO2 interface has been well studied and is known to have relatively few defects. By contrast many metal–insulator interfaces contain significant levels of defects which can lead to fermi-level pinning, charging, or other phenomena that ultimately degrade device performance.

- In the MOSFET IC fabrication process, it is preferable to deposit the gate material prior to certain high-temperature steps in order to make better performing transistors. Such high temperature steps would melt some metals, limiting the types of metals that could be used in a metal-gate based process.

While polysilicon gates have been the defacto standard for the last twenty years, they do have some disadvantages, which have led to the announcement of their replacement by metal gates. These disadvantages include:

- Polysilicon is not a great conductor (approximately 1000 times more resistive than metals) which reduces the signal propagation speed through the material. The resistivity can be lowered by increasing the level of doping, but even highly doped polysilicon is not as conductive as most metals. In order to improve conductivity further, sometimes a high temperature metal such as tungsten, titanium, cobalt, and more recently nickel, is alloyed with the top layers of the polysilicon. Such a blended material is called silicide. The silicide-polysilicon combination has better electrical properties than polysilicon alone and still does not melt in subsequent processing. Also the threshold voltage is not significantly higher than polysilicon alone, because the silicide material is not near the channel. The process in which silicide is formed on both the gate electrode and the source and drain regions is sometimes called salicide, self-aligned silicide.

- When the transistors are extremely scaled down, it is necessary to make the gate dielectric layer very thin, around 1 nm in state-of-the-art technologies. A phenomenon observed here is the so-called poly depletion, where a depletion layer is formed in the gate polysilicon layer next to the gate dielectric when the transistor is in the inversion. To avoid this problem a metal gate is desired. A variety of metal gates such as tantalum, tungsten, tantalum nitride, and titanium nitride are used, usually in conjunction with high-k dielectrics. An alternative is to use fully-silicided polysilicon gates, and the process is referred to as FUSI.

Multigate Device

[edit | edit source]A multigate device or Multigate Field Effect Transistor(MuGFET) refers to a MOSFET which incorporates more than one gate into a single device. The multiple gates may be controlled by a single gate electrode, wherein the multiple gate surfaces act electrically a single gate, or by independent gate electrodes. A multigate device employing independent gate electrodes is sometimes called a Multiple Independent Gate Field Effect Transistor or MIGFET. Multigate transistors are one of several strategies being developed by CMOS semiconductor manufacturers to create ever-smaller microprocessors and memory cells, colloquially referred to as extending Moore's Law. Development efforts into multigate transistors have been reported by AMD, Hitachi, IBM, Infineon, Intel, TSMC, UC Berkeley and others and the ITRS predicts that such devices will be the cornerstone of sub-32 nm technologies. The primary roadblock to widespread implementation is manufacturability, as both planar and non-planar designs present significant challenges, especially with respect to lithography and patterning. Other complementary strategies for device scaling include channel strain engineering, silicon-on-insulator-based technologies, and high-k/metal gate materials.

FinFET

[edit | edit source]The term FinFET was coined by University of California, Berkeley researchers to describe a nonplanar, double-gate transistor built on an SOI susbtrate, based on the earlier DELTA (single-gate) transistor design. The distinguishing characteristic of the FinFET is that the conducting channel is wrapped around a thin silicon "fin", which forms the body of the device. The dimensions of the fin determine the effective channel length of the device.

In current usage the term FinFET has a less precise definition. Among microprocessor manufacturers, AMD, IBM, and Motorola describe their double-gate development efforts as FinFET development whereas Intel avoids using the term to describe their closely related tri-gate[1] architecture. In the technical literature, FinFET is used somewhat generically to describe any fin-based, multigate transistor architecture regardless of number of gates.

A 25-nm transistor operating on just 0.7 Volt was demonstrated in December 2002 by Taiwan Semiconductor Manufacturing Company. The "Omega FinFET" design, named after the similarity between the Greek letter "Omega" and the shape in which the gate wraps around the source/drain structure, has a gate delay of just 0.39 picosecond (ps) for the N-type transistor and 0.88 ps for the P-type.

Plasma Etching

[edit | edit source]Plasma etching is a form of plasma processing in which a high-speed stream of plasma is shot (in pulses) at a sample. The atoms of the shot element embed themselves at or just below the surface of the target. The physical properties of the target are modified in the process. Plasma systems ionize a variety of source gases in a vacuum system by using RF excitations. The frequency of operation of the RF power source is frequently of 13.56 MHz, chosen by the Federal Communications Commission (FCC) for industrial and scientific use. Nevertheless, it can be used lower frequencies (kilohertz) or higher (microwave). The mode of operation of the plasma system change if the operating pressure change. Also, it is different for different structures of the reaction chamber. Standard plasma etching work with very high pressures. In the simple case, the electrode structure is symmetrical, and the sample is placed upon the grounded electrode. Free radicals such as fluorine or chlorine are created in the plasma and react at the sample surface.

Deep Reactive-Ion Etching

[edit | edit source]

Deep reactive-ion etching (DRIE) is a highly anisotropic etch process used to create deep, steep-sided holes and trenches in wafers, with aspect ratios of 20:1 or more. It was developed for microelectromechanical systems (MEMS), which require these features, but is also used to excavate trenches for high-density capacitors for DRAM.

There are two main technologies for high-rate DRIE: cryogenic and Bosch. Both Bosch and cryo processes can fabricate 90° (truly vertical) walls, but often the walls are slightly tapered, e.g. 88° or 92° ("retrograde").

Another mechanism is sidewall passivation: SiOxFy functional groups (which originate from sulphur hexafluoride and oxygen etch gases) condensate on the sidewalls, and protect them from lateral etching. As a combination of these processes deep vertical structures can be made.

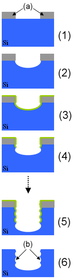

Bosch Process

[edit | edit source]The Bosch process, also known as pulsed or time-multiplexed etching, alternates repeatedly between two modes to achieve nearly vertical structures.

1. A standard, nearly isotropic plasma etch. The plasma contains some ions, which attack the wafer from a nearly vertical direction. (For silicon, this often uses sulfur hexafluoride [SF6].)

2. Deposition of a chemically inert passivation layer. (For instance, C4F8 source gas yields a substance similar to Teflon.)

Each phase lasts for several seconds. The passivation layer protects the entire substrate from further chemical attack and prevents further etching. However, during the etching phase, the directional ions that bombard the substrate attack the passivation layer at the bottom of the trench (but not along the sides). They collide with it and sputter it off, exposing the substrate to the chemical etchant.

These etch/deposit steps are repeated many times over resulting in a large number of very small isotropic etch steps taking place only at the bottom of the etched pits. To etch through a 0.5 mm silicon wafer, for example, 100–1000 etch/deposit steps are needed. The two-phase process causes the sidewalls to undulate with an amplitude of about 100–500 nm. The cycle time can be adjusted: short cycles yield smoother walls, and long cycles yield a higher etch rate.

Applications

[edit | edit source]RIE "deepness" depends on application:

- in DRAM memory circuits, capacitor trenches may be 10–20 µm deep,

- in MEMS, DRIE is used for anything from a few micrometers to 0.5 mm.

What distinguishes DRIE from RIE is etch depth: Practical etch depths for RIE (as used in IC manufacturing) would be limited to around 10µm at a rate up to 1µm/min, while DRIE can etch featues much greater, up to 600µm or more with rates up to 20µ/min.

DRIE of glass requires high plasma power, which makes it difficult to find suitable mask materials for truly deep etching. Polysilicon and nickel are used successfully for 10–50 µm etched depths. In DRIE of polymers, Bosch process with alternating steps of oxygen etching and C4F8 passivation take place. Metal masks can be used.