Materials Science and Engineering/Doctoral review questions/Daily Discussion Topics/01162008

Crystal Growth

[edit | edit source]Why does crystal grow faster in one direction relative to another?

- Kinks may form in one direction

- The growth velocity is resultingly faster

- The ledge direction may be in the same direction as growth

- Kinks may form in one direction, and the ledges need to terminate

- Terrace plane intersects the ledge

BJT Structure

[edit | edit source]SOI

[edit | edit source]Silicon on insulator technology (SOI) refers to the use of a layered silicon-insulator-silicon substrate in place of conventional silicon substrates in semiconductor manufacturing, especially microelectronics, to reduce parasitic device capacitance and thereby improve performance. SOI-based devices differ from conventional silicon-built devices in that the silicon junction is above an electrical insulator, typically silicon dioxide or (less commonly) sapphire. The choice of insulator depends largely on intended application, with sapphire being used for radiation-sensitive applications and silicon oxide preferred for improved performance and diminished short channel effects in microelectronics devices. The precise thickness of the insulating layer and topmost silicon layer also vary widely with application. The first implementation of SOI was announced by IBM in August 1998.

Manufacture of SOI wafers

[edit | edit source]SiO2-based SOI wafers can be produced by several methods:

- SIMOX - Separation by IMplantation of OXygen - uses an oxygen ion beam implantation process followed by high temperature annealing to create a buried SiO2 layer.

- Wafer Bonding - the insulating layer is formed by directly bonding oxidized silicon with a second substrate. The majority of the second substrate is subsequently removed, the remnants forming the topmost Si layer.

- One prominent example of a wafer bonding process is the Smart Cut™ method developed by the French firm Soitec which uses ion implantation followed by controlled exfoliation to determine the thickness of the uppermost silicon layer.

- NanoCleave™ is a technology developed by Silicon Genesis Corporation that separates the silicon via stress at the interface of silicon and silicon-germanium alloy.

- ELTRAN™ is a technology developed by Canon which spouts porous silicon and water cut.

- Seed methods - wherein the topmost Si layer is grown directly on the insulator. Seed methods require some sort of template for homoepitaxy, which may be achieved by chemical treatment of the insulator, an appropriately oriented crystalline insulator, or vias through the insulator from the underlying substrate.

Short-Channel Effect in MOSFET

[edit | edit source]

The use of SOI structures helps to avoid leakage mechanisms in MOSFETS. The device "pinches off" when the voltage is large and the channel width is small. There are several types of short-channel effects that are explained in Pierret.

Reverse Short-Channel Effect

[edit | edit source]The reverse short-channel effect is a secondary effect describing the reduction in threshold voltage Vth in MOSFETs with nonuniformly doped channel regions as the gate length increases. Since drive current is primarily determined by Vth, longer channel devices have more driving ability.

Reverse short channel effect (RSCE) is a result of non-uniform channel doping (halo doping ) in modern processes. To combat drain-induced barrier lowering (DIBL), MOSFET channels are more doped near the source and drain terminals to reduce the size of the depletion region in the vicinity of these junctions (called halo doping to describe the linmitation of this heavy doping to the immediate vicinity of the junctions). At short channel lengths the halo doping of the source overlaps that of the drain, increasing the average channel doping concentration, and thus increasing the threshold voltage. This increased threshold voltage requires a larger gate voltage for channel inversion. However, as channel length is increased, the halo doped regions become separated and the doping midchannel approaches a lower background level dictated by the body doping. This reduction in average channel doping concentration means Vth initially is reduced as channel length increases, but approaches a constant value independent of channel length for large enough lengths.

E-Beam Source and Knudsen Source

[edit | edit source]

E-Beam Source

[edit | edit source]In an EBPVD system, the deposition chamber is evacuated to a pressure of 10-4 Torr. The material to be evaporated is in the form of ingots. There are as many as six electron guns, each having a power from few tens to hundreds of kW. Electron beams can be generated by thermionic emission, field emission or the anodic arc method. The generated electron beam is accelerated to a high kinetic energy and focused towards the ingot. When the accelerating voltage is between 20 kV – 25 kV and the beam current is a few amperes, 85% of the kinetic energy of the electrons is converted into thermal energy as the beam bombards the surface of the ingot. The surface temperature of the ingot increases resulting in the formation of a liquid melt. Although some of incident electron energy is lost in the excitation of X-rays and secondary emission, the liquid ingot material evaporates under vacuum.

The ingot itself is enclosed in a copper crucible, which is cooled by water circulation. The level of molten liquid pool on the surface of the ingot is kept constant by vertical displacement of the ingot. The number of ingot feeders depends upon the material to be deposited. The evaporation rate may be of the order of 10-2 g/cm2 sec.

Knudsen Source

[edit | edit source]In crystal growth, knudsen cells are often used as sources evaporators for relatively low partial pressure elementary sources, e.g., Ga, Al, Hg, As, etc. It is easy to control the temperature of evaporating content and commonly used in Molecular-beam epitaxy.

A typical Knudsen cell contains a crucible (made of pyrolytic Boron Nitride, quartz, tungsten or graphite), heating filaments (often made of metal Tantalum), water cooling system, heat shields and orifice shutter.

Disruptive devices

[edit | edit source]A disruptive device is a device that has a dielectric, whereupon being stressed beyond its dielectric strength, has an electrical breakdown. This results in the sudden transition of part of the dielectric material from an insulating state to a highly conductive state. This transition is characterized by the formation of an electric spark, and possibly an electric arc through the material. If this occurs within a solid dielectric, physical and chemical changes along the path of the discharge will cause permanent degradation and significant reduction in the material's dielectric strength.

Silicides

[edit | edit source]Silicon atoms in silicides can have many possible organizations:

- Isolated silicon atoms: electrically conductive Cu5Si, (V,Cr,Mn)3Si, Fe3Si, Mn3Si, and nonconductive (Mg,Ge,Sn,Pb)2Si, (Ca,Ru,Ce,Rh,Ir,Ni)2Si)

- Si2 pairs: U3Si2, Hf and Th silicides

- Si4 tetrahedra: KSi, RbSi, CsSi

- Sin chains: USi, (Ti, Zr, Hf, Th, Ce, Pu)Si, CaSi, SrSi, YSi

- Planar hexagonal graphite-like Si layers: β-USi2, silicides of other lanthanoids and actinoids

- Corrugated hexagonal Si layers: CaSi2

- Open three-dimensional Si skeletons: SrSi2, ThSi2, α-USi2

Group 1 and 2 silicides e.g. Na2Si and Ca2Si react with water to yielding hydrogen and/or silanes. The transition metal silicides are, in contrast, usually inert to aqueous solutions of everything with exception of hydrofluoric acid; however, they react with more aggressive agents, eg. melted potassium hydroxide, or fluorine and chlorine when red-hot.

Silicide prepared by a self-aligned process is called salicide. This is a process in which silicide contacts are formed only in those areas in which deposited metal (which after annealing becomes a metal component of the silicide) is in direct contact with silicon, hence, the process is self-aligned. It is commonly implemented in MOS/CMOS processes for ohmic contacts of the source, drain, and poly-Si gate.

Types of chemical vapor deposition

[edit | edit source]A number of forms of CVD are in wide use and are frequently referenced in the literature. These processes differ in the means by which chemical reactions are initiated (e.g., activation process) and process conditions.

- Classified by operating pressure

- Atmospheric pressure CVD (APCVD) - CVD processes at atmospheric pressure.

- Low-pressure CVD (LPCVD) - CVD processes at subatmospheric pressures. Reduced pressures tend to reduce unwanted gas-phase reactions and improve film uniformity across the wafer. Most modern CVD process are either LPCVD or UHVCVD.

- Ultrahigh vacuum CVD (UHVCVD) - CVD processes at a very low pressure, typically below 10-6 Pa (~ 10-8 torr). Caution: in other fields, a lower division between high and ultra-high vacuum is common, often 10-7 Pa.

- Classified by physical characteristics of vapor

- Aerosol assisted CVD (AACVD) - A CVD process in which the precursors are transported to the substrate by means of a liquid/gas aerosol, which can be generated ultrasonically. This technique is suitable for use with involatile precursors.

- Direct liquid injection CVD (DLICVD) - A CVD process in which the precursors are in liquid form (liquid or solid dissolved in a convenient solvent). Liquid solutions are injected in a vaporization chamber towards injectors (typically car injectors). Then the precursors vapours are transported to the substrate as in classical CVD process. This technique is suitable for use on liquid or solid precursors. High growth rates can be reached using this technique.

- Plasma methods (see also Plasma processing)

- Microwave plasma-assisted CVD (MPCVD)

- Plasma-Enhanced CVD (PECVD) - CVD processes that utilize a plasma to enhance chemical reaction rates of the precursors. PECVD processing allows deposition at lower temperatures, which is often critical in the manufacture of semiconductors.

- Remote plasma-enhanced CVD (RPECVD) - Similar to PECVD except that the wafer substrate is not directly in the plasma discharge region. Removing the wafer from the plasma region allows processing temperatures down to room temperature.

- Atomic layer CVD (ALCVD) – Deposits successive layers of different substances to produce layered, crystalline films. See Atomic layer epitaxy.

- Hot wire CVD (HWCVD) - Also known as Catalytic CVD (Cat-CVD) or hot filament CVD (HFCVD). Uses a hot filament to chemically decompose the source gases.

- Metalorganic chemical vapor deposition (MOCVD) - CVD processes based on metalorganic precursors.

- Hybrid Physical-Chemical Vapor Deposition (HPCVD) - Vapor deposition processes that involve both chemical decomposition of precursor gas and physical evaporation of solid source.

- Rapid thermal CVD (RTCVD) - CVD processes that use heating lamps or other methods to rapidly heat the wafer substrate. Heating only the substrate rather than the gas or chamber walls helps reduce unwanted gas phase reactions that can lead to particle formation.

- Vapor phase epitaxy (VPE)

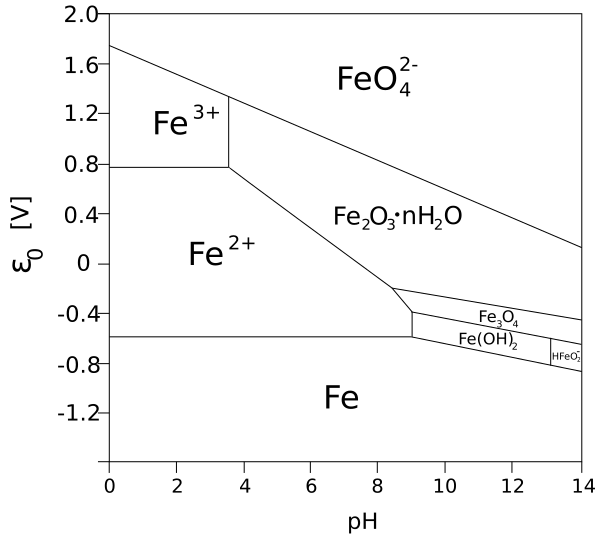

Pourbaix Diagrams

[edit | edit source]

In chemistry, a Pourbaix diagram, also known as a potential/pH diagram, maps out possible stable (Chemical equilibrium) phases of an aqueous electrochemical system. Predominant ion boundaries are represented by lines. As such a Pourbaix diagram can be read much like a standard phase diagram with a different set of axes.

The diagrams are named after Marcel Pourbaix (1904–1998), the Russian-born chemist who invented them.

Pourbaix Diagrams are also known as Eh-pH diagrams due to the labeling of the two axes. The vertical axis is labeled Eh for the voltage potential as calculated by the Nernst equation.

The horizontal axis is labeled pH for the -log function of the H+ ion concentration.

Such diagrams can be drawn for any chemical system, it is important to note that the addition of a metal binding agent (ligand) will often modify the diagram. For instance carbonate has a great effect upon the diagram for uranium.

![{\displaystyle Eh=E^{0}+{\frac {0.0592}{n}}\ Log{\frac {[C]^{c}[D]^{d}}{[A]^{a}[B]^{b}}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/7ff1b565444552984c0ba0bf3ffe06368d36e355)

![{\displaystyle pH=-Log[H^{+}]\;}](https://wikimedia.org/api/rest_v1/media/math/render/svg/d899f493d6b4bb6ab304a9179750f07e565e56c1)