Materials Science and Engineering/Diagrams/Semiconductor Devices

Energy Band Diagram

[edit | edit source]

In solid-state physics of semiconductors, a band diagram is a diagram showing the variation in the valence band and conduction band edges vs. some spatial dimension, often denoted x. The Fermi level is also usually indicated in the diagram. Sometimes the intrinsic Fermi energy, Ei, which the Fermi level in the absence of doping, may be shown also. The work function and electron affinity are shown on some diagrams as well. These diagrams are useful in explaining the operation of many kinds of semiconductor devices.

Metals have unfilled valence band, or greatly overlapping valence and conduction bands. Semimetals have a small overlap between valence and conduction bands, whereas semiconductors have a small band gap between them. The Fermi level is located in the middle of the band gap for an undoped semiconductor. Insulators have a large band gap, so that electrons cannot escape the valence band to enter the conduction band.

Thermal Oxidation

[edit | edit source]

In microfabrication, thermal oxidation is a way to produce a thin layer of oxide (usually silicon dioxide) on the surface of a wafer (semiconductor). The technique forces an oxidizing agent to diffuse into the wafer at high temperature and react with it. The rate of oxide growth is often predicted by the Deal-Grove model.

Thermal oxidation of silicon is usually performed at a temperature between 800 and 1200°C. It may use either water vapor (steam) or molecular oxygen as the oxidant; it is consequently called either wet or dry oxidation. The reaction is one of the following:

Most thermal oxidation is performed in furnaces, at temperatures between 800 and 1200°C. A single furnace accepts many wafers at the same time, in a specially designed quartz rack (called a "boat"). Historically, the boat entered the oxidation chamber from the side (this design is called "horizontal"), and held the wafers vertically, beside each other. However, many modern designs hold the wafers horizontally, above and below each other, and load them into the oxidation chamber from below.

Vertical furnaces stand higher than horizontal furnaces, so they may not fit into some microfabrication facilities. However, they help to prevent dust contamination. Unlike horizontal furnaces, in which falling dust can contaminate any wafer, vertical furnaces only allow it to fall on the top wafer in the boat.

Vertical furnaces also eliminate an issue that plagued horizontal furnaces, uniformity of grown oxide across the wafer. Horizontal furnaces typically have convection currents inside the tube which causes the bottom of the tube to be slightly colder than the top of the tube. As the wafers lie vertically in the tube the convection and the temperature gradient with it causes the top of the wafer to have a thicker oxide than the bottom of the wafer. Vertical furnaces solve this problem by having wafer sitting horizontally, and then having the gas flow in the furnace flowing from top to bottom, significantly dampening any thermal convections.

Vertical furnaces also allow the use of load locks to purge the wafers with nitrogen before oxidation to limit the growth of native oxide on the Si surface.

Rate of Oxidation

[edit | edit source]Consider four fluxes:

Consider the relative magnitude of the fluxes:

Expression of is similar to that found in CVD model

The term is the gas phase mass transfer coefficient

The boundary layer thickness is

Assume that the ratio of oxidant in the vapor phase to oxidant in solution is described by the segregation coefficient,

Assume there is equilibrium at the gas-solid interface

Set equal to the concentration of the oxidant that would be in equilibrium with gas phase at pressure

Assume that the surface reaction is

- thermally activated

- first order

- in the linear response regime

Set

is the number of oxidant molecules per unit volume of the oxide. If ,

If ,

Surface Reaction Limited

Diffusion Limited

Generally,

Parabolic:

Linear:

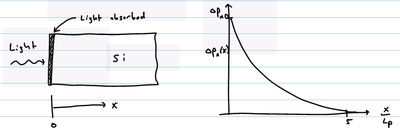

Light Absorption in Silicon

[edit | edit source]

Under steady state conditions, with , the diffusion equation of holes is of the form below with .

The equation can be solved with the boundary conditions below

and

A general solution is copied below

The boundary condition yields the following result

Metallurgical Junction

[edit | edit source]Diffusion Profile

[edit | edit source]Voltage, Electric Field, and Charge Density

[edit | edit source]

The electrostatic potential at a given point is expressed as below.

The potential energy is also the difference in energy between the energy of the conduction band and the reference energy.

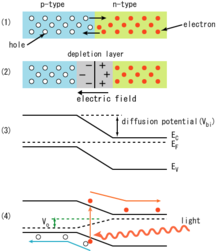

PN Junction

[edit | edit source]

The p-n junction possesses some interesting properties which have useful applications in modern electronics. P-doped semiconductor is relatively conductive. The same is true of N-doped semiconductor, but the junction between them is a nonconductor. This nonconducting layer, called the depletion zone, occurs because the electrical charge carriers in doped n-type and p-type silicon (electrons and holes, respectively) attract and eliminate each other in a process called recombination. By manipulating this nonconductive layer, p-n junctions are commonly used as diodes: electrical switches that allow a flow of electricity in one direction but not in the other (opposite) direction. This property is explained in terms of the forward-bias and reverse-bias effects, where the term bias refers to an application of electric voltage to the p-n junction.

A common type of transistor, the bipolar junction transistor, consists of two p-n junctions in series, for example in the form n-p-n; no current can flow through it unless a separate small voltage is applied to the middle layer. The most common type of solar cell is basically a large p-n junction; the free carrier pairs created by light energy are separated by the junction and contribute to current.

Forward Bias

[edit | edit source]Forward-bias occurs when the P-type semiconductor material is connected to the positive terminal of a battery and the N-type semiconductor material is connected to the negative terminal, as shown below.

With a battery connected this way, the holes in the P-type region and the electrons in the N-type region are pushed towards the junction. This reduces the width of the depletion zone. The positive charge applied to the P-type material repels the holes, while the negative charge applied to the N-type material repels the electrons. As electrons and holes are pushed towards the junction, the distance between them decreases. This lowers the barrier in potential. With increasing forward-bias voltage, the depletion zone eventually becomes thin enough that the zone's electric field can't counteract majority charge carrier motion (physics) across the p-n junction, consequently reducing electrical resistance. The electrons (or holes) which cross the p-n junction into the P-type material (or into the N-type material for holes) will diffuse in the near-neutral region. Therefore, the amount of minority diffusion in the near-neutral zones determines the amount of current that may flow through the diode.

Reverse Bias

[edit | edit source]Connecting the P-type region to the negative terminal of the battery and the N-type region to the positive terminal, produces the reverse-bias effect. The connections are illustrated in the following diagram:

Because the P-type material is now connected to the negative terminal of the power supply, the 'holes' in the P-type material are pulled away from the junction, causing the width of the depletion zone to increase. Similarly, because the N-type region is connected to the positive terminal, the electrons will also be pulled away from the junction. Therefore the depletion region widens, and does so increasingly with increasing reverse-bias voltage. This increases the voltage barrier causing a high resistance to the flow of charge carriers thus allowing minimal electric current to cross the p-n junction.

Bipolar Junction Transistor

[edit | edit source]

An NPN transistor can be considered as two diodes with a shared anode region. In typical operation, the emitter–base junction is forward biased and the base–collector junction is reverse biased. In an NPN transistor, for example, when a positive voltage is applied to the base–emitter junction, the equilibrium between thermally generated carriers and the repelling electric field of the depletion region becomes unbalanced, allowing thermally excited electrons to inject into the base region. These electrons wander (or "diffuse") through the base from the region of high concentration near the emitter towards the region of low concentration near the collector. The electrons in the base are called minority carriers because the base is doped p-type which would make holes the majority carrier in the base.

MOS

[edit | edit source]

A traditional metal–oxide–semiconductor (MOS) structure is obtained by depositing a layer of silicon dioxide (SiO2) and a layer of metal (polycrystalline silicon is commonly used instead of metal) on top of a semiconductor die. As the silicon dioxide is a dielectric material its structure is equivalent to a planar capacitor, with one of the electrodes replaced by a semiconductor.

When a voltage is applied across a MOS structure, it modifies the distribution of charges in the semiconductor. If we consider a P-type semiconductor (with NA the density of acceptors, p the density of holes; p = NA in neutral bulk), a positive voltage, VGB, from gate to body (see figure) creates a depletion layer by forcing the positively charged holes away from the gate-insulator/semiconductor interface, leaving exposed a carrier-free region of immobile, negatively charged acceptor ions. See doping (semiconductor). If VGB is high enough, a high concentration of negative charge carriers forms in an inversion layer located in a thin layer next to the interface between the semiconductor and the insulator. (Unlike the MOSFET, discussed below, where the inversion layer electrons are supplied rapidly from the source/drain electrodes, in the MOS capacitor they are produced much more slowly by thermal generation through carrier generation and recombination centers in the depletion region.) Conventionally, the gate voltage at which the volume density of electrons in the inversion layer is the same as the volume density of holes in the body is called the threshold voltage.

This structure with P-type body is the basis of the N-type MOSFET, which requires the addition of an N-type source and drain regions.

MOSFET

[edit | edit source]

The metal–oxide–semiconductor field-effect transistor (MOSFET, MOS-FET, or MOS FET) is by far the most common field-effect transistor in both digital and analog circuits. The MOSFET is composed of a channel of n-type or p-type semiconductor material (see article on semiconductor devices), and is accordingly called an NMOSFET or a PMOSFET (also commonly nMOSFET, pMOSFET).

The 'metal' in the name is now often a misnomer because the previously metal gate material is now a layer of polysilicon (polycrystalline silicon; why polysilicon is used will be explained below). Previously aluminium was used as the gate material until the 1980s when polysilicon became dominant, owing to its capability to form self-aligned gates.

To overcome power consumption increase due to gate current leakage, high-κ dielectric is replacing silicon dioxide as the gate insulator, and metal gates are making a comeback by replacing polysilicon.

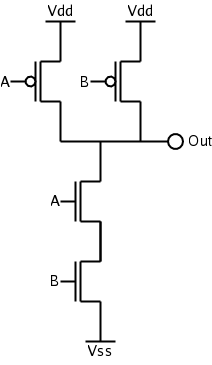

CMOS

[edit | edit source]

Complementary metal–oxide–semiconductor (CMOS) (pronounced "see-moss", IPA: /siːmɔːs, ˈsiːmɒs/), is a major class of integrated circuits. CMOS technology is used in microprocessors, microcontrollers, static RAM, and other digital logic circuits. CMOS technology is also used for a wide variety of analog circuits such as image sensors, data converters, and highly integrated transceivers for many types of communication.

CMOS is also sometimes referred to as complementary-symmetry metal–oxide–semiconductor. The words "complementary-symmetry" refer to the fact that the typical digital design style with CMOS uses complementary and symmetrical pairs of p-type and n-type metal oxide semiconductor field effect transistors (MOSFETs) for logic functions.

Two important characteristics of CMOS devices are high noise immunity and low static power consumption. Significant power is only drawn when the transistors in the CMOS device are switching between on and off states. Consequently, CMOS devices do not produce as much waste heat as other forms of logic, for example transistor-transistor logic (TTL). CMOS also allows a high density of logic functions on a chip.

The phrase "metal–oxide–semiconductor" is a reference to the physical structure of certain field-effect transistors, having a metal gate electrode placed on top of an oxide insulator, which in turn is on top of a semiconductor material. Instead of metal, current gate electrodes (including those up to the 65 nanometer technology node) are almost always made from a different material, polysilicon, but the terms MOS and CMOS nevertheless continue to be used for the modern descendants of the original process. Metal gates have made a comeback with the advent of high-k dielectric materials in the CMOS process, as announced by IBM and Intel for the 45 nanometer node and beyond

MESFET

[edit | edit source]

MESFET stands for Metal-Semiconductor Field Effect Transistor. It is quite similar to a JFET in construction and terminology. The difference is that instead of a using a p-n junction for a gate, a Schottky (metal-semiconductor) junction is used. MESFETs are usually constructed in compound semiconductor technologies lacking high quality surface passivation such as GaAs, InP, or SiC, and are faster but more expensive than silicon-based JFETs or MOSFETs. Production MESFETs are operated up to approximately 30 GHz, and are commonly used for microwave frequency communications and radar. From a digital circuit design perspective, it is increasingly difficult to use MESFETs as the basis for digital integrated circuits as the scale of integration goes up, compared to CMOS silicon based fabrication.

The MESFET differs from the common insulated gate FET in that there is no insulator under the gate over the active switching region. This implies that the MESFET gate should, in transistor mode, be biased such that one does not have a forward conducting metal semiconductor diode instead of a reversed biased depletion zone controlling the underlying channel. While this restriction inhibits certain circuit possibilities, MESFET analog and digital devices work reasonably well if kept within the confines of design limits. The most critical aspect of the design is the gate metal extent over the switching region. Generally the narrower the gate modulated carrier channel the better the frequency handling abilities, overall. Spacing of the source and drain with respect to the gate, and the lateral extent of the gate are important though somewhat less critical design parameters. MESFET current handling ability improves as the gate is elongated laterally, keeping the active region constant, however is limited by phase shift along the gate due to the transmission line effect. As a result most production MESFETs use a built up top layer of low resistance metal on the gate, often producing a mushroom-like profile in cross section.

FinFET

[edit | edit source]

The term FinFET was coined by University of California, Berkeley researchers to describe a nonplanar, double-gate transistor built on an SOI susbtrate, based on the earlier DELTA (single-gate) transistor design. The distinguishing characteristic of the FinFET is that the conducting channel is wrapped around a thin silicon "fin", which forms the body of the device. The dimensions of the fin determine the effective channel length of the device.

In current usage the term FinFET has a less precise definition. Among microprocessor manufacturers, AMD, IBM, and Motorola describe their double-gate development efforts as FinFET development whereas Intel avoids using the term to describe their closely related tri-gate[1] architecture. In the technical literature, FinFET is used somewhat generically to describe any fin-based, multigate transistor architecture regardless of number of gates.

A 25-nm transistor operating on just 0.7 Volt was demonstrated in December 2002 by Taiwan Semiconductor Manufacturing Company. The "Omega FinFET" design, named after the similarity between the Greek letter "Omega" and the shape in which the gate wraps around the source/drain structure, has a gate delay of just 0.39 picosecond (ps) for the N-type transistor and 0.88 ps for the P-type.

Solar Cell

[edit | edit source]

A solar cell or photovoltaic cell is a device that converts light energy into electrical energy by the photovoltaic effect. Photovoltaics is the field of technology and research related to the application of solar cells as solar energy. Sometimes the term solar cell is reserved for devices intended specifically to capture energy from sunlight, while the term photovoltaic cell is used when the source is unspecified.

Assemblies of cells are used to make solar modules, which may in turn be linked in photovoltaic arrays.

Solar cells have many applications. Individual cells are used for powering small devices such as electronic calculators. Photovoltaic arrays generate a form of renewable electricity, particularly useful in situations where electrical power from the grid is unavailable such as in remote area power systems, Earth-orbiting satellites and space probes, remote radiotelephones and water pumping applications. Photovoltaic electricity is also increasingly deployed in grid-tied electrical systems.

LED

[edit | edit source]A light-emitting diode (LED) is a semiconductor diode that emits incoherent narrow-spectrum light when electrically biased in the forward direction of the p-n junction, as in the common LED circuit. This effect is a form of electroluminescence.

An LED is usually a small area source, often with extra optics added to the chip that shapes its radiation pattern. LED's are often used as small indicator lights on electronic devices and increasingly in higher power applications such as flashlights and area lighting. The color of the emitted light depends on the composition and condition of the semiconducting material used, and can be infrared, visible, or near-ultraviolet. An LED can be used as a regular household light source.

Like a normal diode, an LED consists of a chip of semiconducting material impregnated, or doped, with impurities to create a p-n junction. As in other diodes, current flows easily from the p-side, or anode, to the n-side, or cathode, but not in the reverse direction. Charge-carriers—electrons and holes—flow into the junction from electrodes with different voltages. When an electron meets a hole, it falls into a lower energy level, and releases energy in the form of a photon.

The wavelength of the light emitted, and therefore its color, depends on the band gap energy of the materials forming the p-n junction. In silicon or germanium diodes, the electrons and holes recombine by a non-radiative transition which produces no optical emission, because these are indirect band gap materials. The materials used for an LED have a direct band gap with energies corresponding to near-infrared, visible or near-ultraviolet light.

HEMT

[edit | edit source]

HEMT stands for High Electron Mobility Transistor, and is also called heterostructure FET (HFET) or modulation-doped FET (MODFET). A HEMT is a field effect transistor incorporating a junction between two materials with different band gaps (i.e. a heterojunction) as the channel instead of a doped region, as is generally the case for MOSFETs. A commonly used material combination is GaAs with AlGaAs, though there is wide variation, dependent on the application of the device. Devices incorporating more indium generally show better high-frequency performance, while in recent years, gallium nitride HEMTs have seen a massive increase in research effort, due to their high-power performance.

In general, to allow conduction, semiconductors need to be doped with impurities to generate mobile electrons in the layer. However, this causes electrons to slow down because they end up colliding with the impurities which were used to generate them in the first place. HEMT, however, is a smart device to resolve this seemingly inherent unsolvable contradiction.

HEMT accomplishes this by use of high mobility electrons generated using the heterojunction of a highly-doped wide-bandgap n-type donor-supply layer (AlGaAs in our example) and a non-doped narrow-bandgap channel layer with no dopant impurities (GaAs in this case). The electrons generated in the n-type AlGaAs thin layer drop completely into the GaAs layer to form a depleted AlGaAs layer, because the heterojunction created by different band-gap materials forms a quantum well (a steep canyon) in the conduction band on the GaAs side where the electrons can move quickly without colliding with any impurities because the GaAs layer is undoped, and from which they cannot escape. The effect of this is to create a very thin layer of highly mobile conducting electrons with very high concentration, giving the channel very low resistivity (or to put it another way, "high electron mobility"). This layer is called a two-dimensional electron gas. As with all the other types of FETs, a voltage applied to the gate alters the conductivity of this layer.